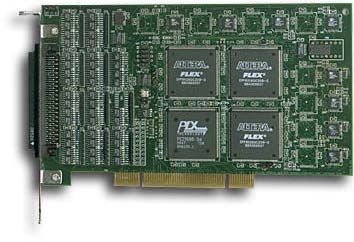

高速数字输入\输出(I/O)卡

生产厂商: 迪阳公司代理

产品型号: PCI-HPDI32A

产品简介: 经RS422/485传输每秒达80M,经ECLI/O传输每秒达200M,经PCI总线传输每秒达132M,缓存,512K

产品简介: 经RS422/485传输每秒达80M,经ECLI/O传输每秒达200M,经PCI总线传输每秒达132M,缓存,512K

| Features | |

| Description | ||

|

|||

北京迪阳世纪科技有限责任公司 版权所有 © 2008 - 2018 著作权声明

010-62156134 62169728 13301007825 节假日:13901042484 微信号:sun62169728

地址:北京市西城阜外百万庄扣钟北里7号公寓

E_mail:sales@pc17.com.cn 传真: 010-68328400

京ICP备17023194号-1 公备110108007750

010-62156134 62169728 13301007825 节假日:13901042484 微信号:sun62169728

地址:北京市西城阜外百万庄扣钟北里7号公寓

E_mail:sales@pc17.com.cn 传真: 010-68328400

京ICP备17023194号-1 公备110108007750

售价:¥0

售价:¥0