使用逻辑分析仪时需要的注意事项

逻辑分析仪提供商已经能让这些设备的速度和功能与工业需求同步,但在很多情况下,从逻辑分析仪到目标系统的物理连接(如探头)可能成为性能瓶颈。

若逻辑分析仪所收到的信号被衰减,那么逻辑分析仪强大的触发和分析工具也变得没有任何意义。本文讨论的问题也是工程师成功连接逻辑分析仪探头所必须了解的基本问题。

几十年来,工程师一直依赖逻辑分析仪,把它们作为主要的系统验证工具。随着科学技术的发展,工程师所设计的数字系统的运行速度不断加快、指令更加复杂,从而也要求更为复杂的分析工具。

探头的外形因子

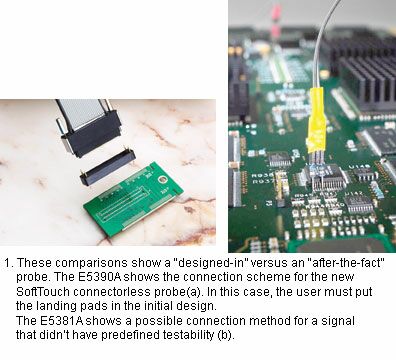

在使用逻辑分析仪时,设计工程师应首先考虑到探头的外形因子的类型。探头的连接可分为两类:一类是“已设计好(designed-in)”的连接,另一类是“事后设计的(after-the-fact)”的连接。

designed-in型逻辑分析仪探头的测试点已被集成到最初设计中,基于连接器的探头或无连接器探头就是采用这种方式。在这种情况下,设计工程师在PCB上设计合适的焊盘,并将待信号连到这些焊盘上,这样逻辑分析仪探头就与待测点有较好互连。

在基于连接器的探头中包含了相互契入的连接器,而无连接器探头则具有连接PCB上焊盘的压缩互连(compression interconnect)(图1a)。

|

after-the-fact型探头应用于可测试性能没有集成到设计中的系统,该系统通过一个包括一系列连接组件(焊接头、接线夹等)的单个探头尖(probe tip)来与待测系统连接。最常见的after-the-fact探头一般利用如图1b所示的“flying-lead(飞线)”探头。

探头的电气负载

任何探头的目标都是给仅给系统带来最小的电气负载。如果探头对系统性能带来太多影响,探头就无法帮助设计工程师验证系统,因为系统故展可能完全是由于探头而引起的。

负载具有产生两个主要影响:首先,它降低目标PCB上的信号质量,导致系统发生失效。其次,它会降低进入逻辑分析仪中被测波形的信号质量──这会在评估时产生消极错误。为了避免这些问题,设计工程师必须了解探头的结构。

探头的阻抗通常很高。探头针(probe tip)电路由一个20kΩ的电阻构成。低频下,探头阻抗等于该电阻的阻值。随着频率的提高,探头内的寄生电容开始降低其阻抗。阻抗根据标准RC响应而变化,这也是目标系统所关注的,因为当探头阻抗接近系统阻抗时,由探头形成的分压器的作用就不能被忽视了。低阻抗将吸收大部分信号并导致系统发生故障。

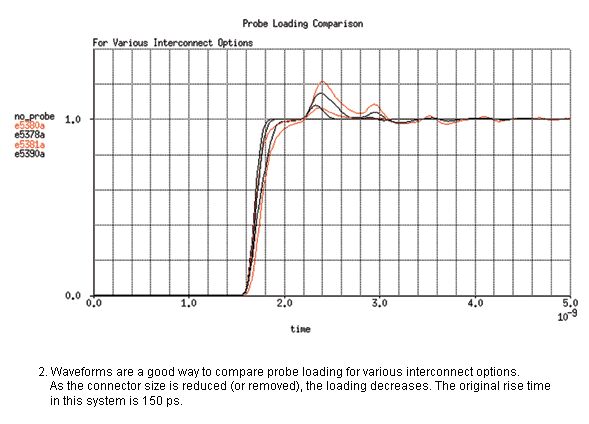

探头的电容大小主要由互相连接的结构决定。例如,若目标信号和探头头的电阻之间有一个非常大的连接器,则这个连接器会给探头负载增加一个大容量的电容。相反,采用小连接器则将减小探头电容。

针对更轻电气负载应用的最新探头是“无连接器”探头。在无连接器探头中,测试焊盘被置于目标系统上。逻辑分析器探头具有连接目标系统的压缩互连特性。通过从电气通道中去除物理连接器,其通道上的电容非常低(见表)。图2显示了多种探头外形因子的等效集总电容,以及这些探头对上升时间为150ps的系统的影响。

|

探头上的信号质量

正如前面提到的,探头尖上的信号质量非常重要,因为它可能导致逻辑分析仪出现错误结果。这也是让验证团队屡屡碰壁的一个原因,因为他们发现他们花了很多时间去调试的问题事实上不存在。为避免出现这种情况,必须考虑到探头尖上的信号质量。

除了减少探头的容性负载外,另外一个重要因素就是探头的位置。在对有多种终端匹配的电路进行探测时,这一点显得更为重要。对于某些终端匹配,接收器所观察到的信号质量已足够好,但该走线上其它任何点上的信号就可能差到不可接受了。

为解释这一点,我们假定有一个带串联终端匹配的传输线。串联终端匹配的原理是感应波形在一瞬间在终端电阻和传输线特征阻抗之间进行分配。幅值为一半的波形沿线传输到接收器。当它到达接收器时,它已经过100%的正反射,使该信号幅值增加1倍,这样就回复到原波形的幅值。反射波以相反的方向传输,直到它被源端的终端电阻吸收,结束瞬时响应。

尽管这样的终端匹配使接收器上的波形非常好,但波形在走线上的每一点都呈阶梯形。阶梯波形并不适于逻辑分析仪,因为在此期间,该波形的幅值只有一半。逻辑分析仪不能分辨出它是逻辑“1”还是逻辑“0”。图3显示了这种情况下的波形。请注意,接收器端的这种波形有较高的信号质量,而探头尖上被测到的波形质量则很是不可接受的。随着信号速度上升,探头尖上的信号质量对成功测量越来越重要。

| ||||||||

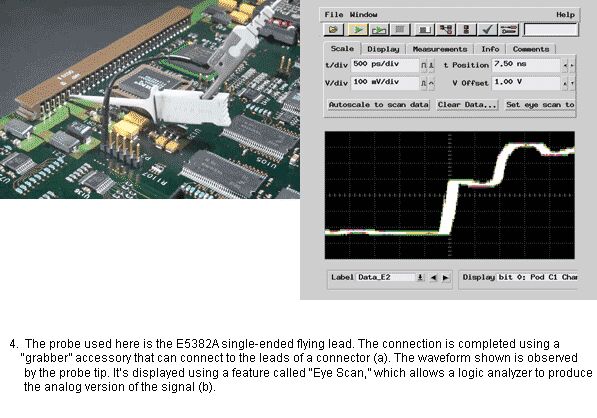

| 接地考虑 没有良好接地是设计工程师进行逻辑分析时另一个容易出问题的地方。探头的地信号为被观察的信号提供一个参考。 因为电流要流动,信号有变化,所以电气信号必须有一个回流电流路径。回流路径常被认为是阻值为0的理想导体。 当其阻值不为0时,在回流路径的阻抗上将产生电压降,从而降低逻辑分析仪测量到的信号幅值。 接地的目的是提供一个具有最小阻抗的回流路径(或接地连接),从而让逻辑分析仪观察到原始的信号幅度。 一个常见的接地问题是地线太长。长地线上的串联电阻会产生压降。为避免这个问题,地线不能比信号线长太多,以便匹配信号和地之间的寄生电阻。 另一个常见的问题是接地回路的自感。当回路由地线和信号线组成时,在接地路径中会形成一个与回路面积成比例的自感。由于电感具有与频率相关的阻抗,它将降低系统的带宽。在高频情况下,这个字感将阻止电荷流过地线,从而减小带宽。 为缓解这类问题,设计工程师应尽量使接地回路尽可能小。当使用基于连接器或无连接器的探头时,接地回路已预先确定。然而,若使用飞线探头,通常使用电线来连接探头和系统,因而形成大的接地回路。 为避免这种回路,将地线和信号线绞合在一起形成一个对绞线。大多数飞线探头现在都有连接附件,已解决这个问题。 当探测时没有采用足够的接地时就会发生另一种情况。在一些探测配置中(如飞线探头),地线数目由使用者决定。为理解这个问题,假定一个飞线设定16个信号线仅用一根地线连接。 此时,所有16根信号线的回流电流必须通过单个地线连接。当1个或2个信号回路通过地线时,地线的自感应足够低,其上的压降不会变大。但若是16根信号线,则回流电流就很大了,此时所产生的地线压降不能忽略。 要解决这一问题就要求增加地线的数量,理想的情况是一根信号线对应一根地线。地线的数量也与频率成比例,但是建议不要用一根地线对应两根以上的信号线。 若操作者在使用逻辑分析仪时不能获得准确的数据,首先要考虑的就是检查地线。 如今有多种探头可供选择,有时很难决定采用哪种连接机制以确保探测成功。在某些情况下,甚至要知道哪些解决方案可用也很困难。下面将讨论当设计工程师采用错误的探测解决方案时常犯的错误。 选择错误的探测点 考虑前面提到的串联终端配置系统,该系统由背板上的驱动IC和采用BGA封装的接收器实现。使用者根据使用的方便,在引脚的背板连接器上对系统进行探测。但是,正如前面已经讨论的那样,在驱动器上探测串联终端配置系统将在逻辑分析仪的探头尖产生一个阶梯波形。图4a显示了探测连接方式,图4b则是通过探头检测到的最终波形。

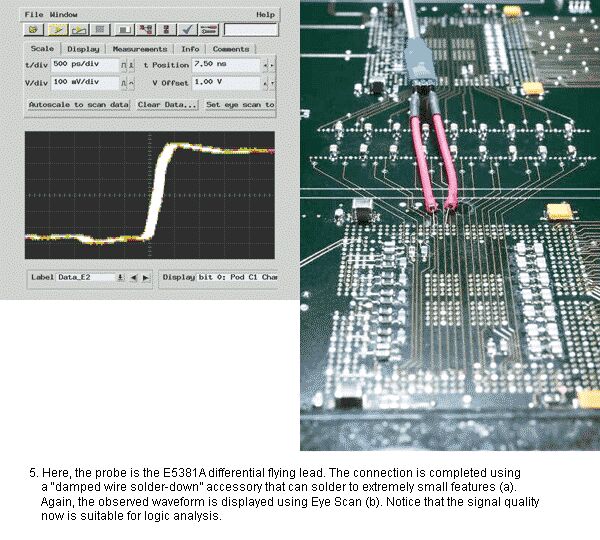

毫无疑问这样的波形是不可接受的。解决的办法是直接在接收器上进行探测。BGA封装最近的物理探测点可能是PCB底面的引线过孔焊盘。图5a展示了一种新的连接方案,它直接用焊料将飞线连接到BGA的引线过孔焊盘。图5b是测试到的信号波形。

使用错误的连接方法 假设用逻辑分析仪观察一个系统的PCB上两个器件之间的信号。该信号走线布在PCB表层,若负载超过3.5pF,则会导致系统失效。设计工程师利用基于Mictor连接器的探头E5380A来观察信号。 由于连接器的管脚分布和结构,信号不能用过它直接连接。这迫使设计工程师将连接器放在走线层,并对每个信号增加过孔。于是,对连接器的走线连接利用另外一层PCB层完成,其走线方向与原始信号的走线垂直。图6显示了该连接器的布线图。

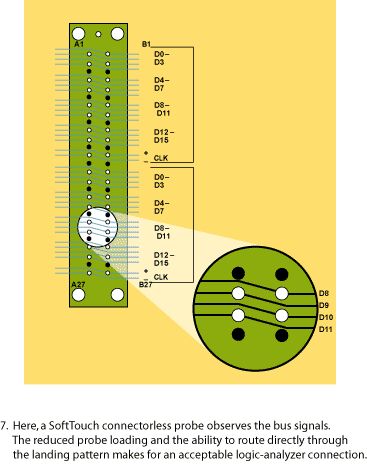

现在考虑一个替代方案,即采用E5390A软接触无连接器探头。此时可将信号连接到探测点的测试焊盘(见图7),这意味着不会给系统增加额外的走线电容。该探头的网络电容为0.7 pF,通过采用这种连接,可在不导致系统失效的情况下进行逻辑分析。

作者:Brock J. LaMeres,Kenneth Johnson,安捷伦科技公司 |

010-62156134 62169728 13301007825 节假日:13901042484 微信号:sun62169728

地址:北京市西城阜外百万庄扣钟北里7号公寓

E_mail:sales@pc17.com.cn 传真: 010-68328400

京ICP备17023194号-1 公备110108007750