# 基于 NIOS 处理器的数字示波表设计

赵贻玖 王厚军 戴志坚

(电子科技大学自动化工程学院 成都 610054)

摘 要 提出了基于 NIOS 处理器的数字示波表的设计原理与实现,介绍了 NIOS 嵌入式 CPU 的结构以及设计基本方法,同时给出了 NIOS 处理器实现数据采集、处理和显示控制的方案。按照该方案设计的数字示波器可以实现高速的数据处理能力和界面控制能力。

关键词 数字示波表 AVALON 总线 NIOS 处理器 FPGA

# Design of a digital oscillograph based on NIOS CPU

Zhao YiJiu Wang Houjun Dai Zhijian

(School of Automation, University of Electronic Science and Technology of China, Chengdu 510054, China)

Abstract The design and the realization of a digital oscillograph based on NIOS CPU are introduced in this paper. It describes the structure of the embedded CPU NIOS and the general method to design a system. It puts forward a technique to realize data acquisition, data processing and display controlling. The digital oscillograph which is designed according to this technique can realize high speed data processing and interface controlling.

Key words digital oscillograph AVALON bus NIOS CPU FPGA

#### 1 引 宮

片上可编程系统(system on a programmable chip, SOPC)是的一种灵活、高效的 SOC(System On a Chip)解决方案。它将处理器、存储器、I/O 口等系统设计需要的功能模块集成到一个 PLD上,构成一个可编程的片上系统。NIOS 处理器就是 FPGA 中嵌入的一个软核,它占芯片很少的一部分逻辑单元。相比传统单片机有处理器速度快(可达上百 M)、系统配置修改方便、可在一个 FPGA 中嵌入多个 NIOS 处理器等优点。NIOS 处理器设计嵌入式系统的流程简单,已经逐渐用到测量仪器中。

数字示波表是一种测量信号波形的测量仪器,具有波形捕获、存储、处理等功能,是最重要的时域测试仪器之一。基于 NIOS 处理器的数字示波表具有高速的数据处理能力和强大的人机界面控制能力,在降低仪器成本的同时性能得到极大的提高。

## 2 基于 NIOS 的数字示波表的基本结构

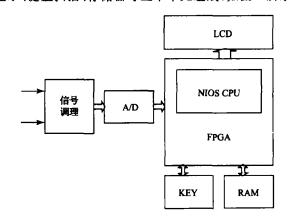

该数字示波表是由数据采样通道、数据处理、波形显示、键盘扫描、存储器等五个单元组成,如图1所示。

图 1 数字示波表原理图

待测信号经信号调理电路后采样,在触发控制电路的控制下存储到 FPGA中的 FIFO 内,以便 CPU 读取。采样控制和触发控制电路设计在一片 Altera 公司

Cyclone 系列的 EP1C6 大规模可编程逻辑器件中,通过图形描述及 VHDL 语言编程实现其复杂的触发和存储控制功能。

## 3 NIOS 处理器的设计

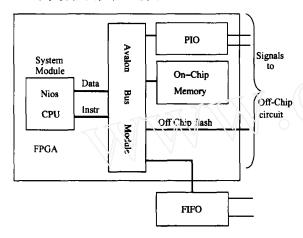

NIOS 处理器选用了 Altera 公司 Cyclone 系列的 EP1C6 FPGA 中嵌入实现, EP1C6 内部集成了 20060 个 LE(逻辑单元), 每个 NIOS 嵌入式处理器占用不到 600 个 LE。在系统设计时可为 NIOS 处理器配置外围设备如串口、存储器、键盘、LCD 显示等接口,它们通过 Avalon 总线与 NIOS CPU 相连。这些都是 FPGA 内部电路配置, 无须修改硬件电路就可完成。NIOS CPU 的系统框图如图 2 所示。

图 2 NIOS CPU 系统框图

NIOS CPU 的所有数据、程序都是通过 Avalon 总 线来传输的,该系统的 FPGA 片外 PIO(外围 IO)包括 一个串行口、显示缓存 RAM、键盘、校准数据和波形数 据储存器(24C256),片内 PIO 是 FIFO。

#### 3.1 NIOS CPU 系统模块设计

嵌入式 NIOS 系统设计流程简单。SOPC Builder 为其提供了一个强大的平台,用于组建一个模块级和 组件级定义的系统。SOPC Builder 的组件库包含了从 简单的固定逻辑的功能模块到复杂的、参数化的、可以 动态生成的子系统等一系列组件。

SOPC Builder 会生成每个硬件部件以及连部件的 片内总线结构,仲裁和中断逻辑。另外,它还能够生成 C和汇编头文件,这些头文件定义了储存器映射、中断优先级和每个外设寄存器空间的数据结构,如果硬件变了 SOPC Builder 会自动更新头文件。

由于所有的模块生成都是以占用 FPGA 逻辑单元 为代价的,而数字示波表的程序庞大,需有比较大的程 序存储空间,这不可能由 FPGA 提供,所以在 FPGA 片外扩展一片 flash 作为程序存储空间。

## 3.2 NIOS CPU 程序设计

NIOS CPU 的所有软件开发任务都是在 Nios II 集成开发环境(IDE)下完成的,并通过 JTAG 下载线 下载到 FPGA 中运行的。数字示波表的程序包括通道 控制、数据读取、数据处理、显示控制和键盘扫描。 NIOS CPU 键盘的阵列扫描来获取用户的设置,根据 不同的档位选择和耦合方式选择来控制通道的放大倍 数和继电器开关,处理器从 FIFO 中读回采样数据并 根据用户的设置要求计算出各种污测参数。NIOS CPU 把处理好的数据发送到显示缓存区以便显示,对 子要储存的波形和设置,处理器在程序的控制下把相 应的标志和数据通过 I2C 总线写人 E2PROM 中。每 次开机时程序都会自动从 E2PROM 中读取通道的校 准数据和上次关机时的设置,然后才进入扫描、读数、 处理、显示的循环程序中。

#### 4 结束语

嵌入式软核技术飞速发展,已经渗透于各个领域和行业。Altera公司的嵌入式软核已经发展到第2代NIOS II,NIOS CPU以其简单的设计流程和可裁减、升级的系统模块化设计降低了产品开发的成本和周期。测试表明,按照该方案设计的数字示波表数据处理快、性能稳定。

#### 参考文献

- [1] 任爱锋,初秀琴,常存,等.基于 FPGA 的嵌入式系统设计[M]. 西安:西安电子科技大学出版社,2004.

- [2] 陈光禹,王厚军,田书林,等.现代电子测试技术[M]. 成都:电子科技大学出版社,2002.

- [3] 潘松,黄继业,曾毓. SOPC 技术实用教程[M]. 北京: 清华大学出版社,2005.