# 高速 ADC 的性能测试

北京理工大学电子工程系(100081) 王卫江 陶 然

摘 要:针对某信号处理机中的高速 A/D 转换器 (ADC) 的应用,利用数字信号处理机的硬件平台,采用纯正弦信号作为输入信号,用数字信号处理器 (DSP) 控制采样,并将 A/D 转换后的数据存储,进行 FFT 变换,进而来分析 ADC 的信噪比及有效位数。该测试方法具有全数字、可编程、精确度高等优点,是较为先进的测试方法。

关键词: AD 转换器 信噪比 有效位数 FFT DSP

目前的实时信号处理机要求 ADC 尽量靠近视频、中频甚至射频,以获取尽可能多的目标信息。因而,ADC 的性能好坏直接影响整个系统指标的高低和性能好坏,从而使得 ADC 的性能测试变得十分重要。

ADC 静态测试的方法已研究多年,国际上已有标准的测试方法,但静态测试不能反映 ADC 的动态特性,因此有必要研究动态测试方法。动态特性包括很多,如信噪比(SNR)、信号与噪声+失真之比(SINAD)、总谐波失真(THD)、无杂散动态范围(SFDR)、双音互调失真(TTIMD)等。本文讨论了利用数字方法对 ADC 的信噪比进行测试,计算出有效位数,并通过测试证明了提高采样频率能改善 SNR,相当于提高了 ADC 的有效位数。在本系统中使用了 AD9224,它是 12 bit、40 MSPS、单 5 V 供电的流水线型低功耗 ADC。

## 1 测试系统原理

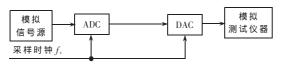

传统的动态测试方法是用高精度 DAC 来重建 ADC 输出信号,然后用模拟方法分析(如图 1 所示)。但这样的测试方法复杂、精度低、能测试的指标有限。国外从 20 世纪 70 年代起研究用数字信号处理技术对 ADC 进行动态测试,主要方法有正弦波拟合法[1]、FFT 法[2-3]、直方图法[4]等,而国内这方面的研究则刚刚起步。

图 1 传统的 ADC 动态特性测试的方法

本文介绍的测试系统是利用作者开发的数字信号处理机中的 DSP 及其仿真系统来进行数据的采集、存储、处理及显示,从而构成可编程、数字化的 ADC 性能测试系统。

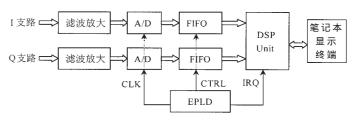

在该信号处理机中,首先采用两路 ADC 进行 I、Q 正交采样;然后用 DSP 并行系统进行数据的 FFT 运算、求模以及恒虚警处理;最后将结果通过并口传给笔记本电脑进行显示。实时信号处理机原理框图如图 2 所示。其中,DSP 芯片是 ADSP21060,主频为 40 MHz。它可以通过 JTAG 接口与 PC 机相连。PC 机上运行 DSP 的在线仿

图 2 实时信号处理机原理框图

真软件,能够实时地控制 DSP 的运行,并将处理结果以数据或图形的方式显示或存储起来。

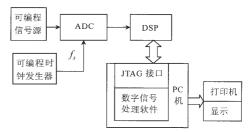

前面讲过,过去对 ADC 进行测试是用模拟方法(如图 1),并且需要高性能的 D/A 转换器。现在则利用计算机进行数字信号处理,可以实现数字化的测试。现取处理机中的一路 ADC 搭建测试系统,如图 3 所示。

图 3 数字化 ADC 测试系统

在本测试系统中,使用信号发生器产生单频正弦信号,f=1.8625MHz。采样频率f,由可编程逻辑器件(EPLD)产生,可产生的采样时钟频率为 3.725MHz 和 7.45MHz 两种,可对正弦信号进行整数倍采样(2 倍和 4 倍)。这里将正弦信号采样数据取为 256 个来进行处理。

## 2 ADC 动态指标

#### 2.1 信噪比

对于理想的 ADC 来说,在奈奎斯特带宽内的噪声电压有效值可表示为  $q/\sqrt{12}$ 。q 表示最低位码的权值,即 ADC 的量化电压,该值与输入信号的幅度和频率无关。对于一个满度的正弦波输入信号,理论上的信噪比(SNR)可表示为:

$$SNR=6.02N+1.76dB+10lg(f_s/2B)$$

(1)

式中, $N$  是 ADC 的位数, $f_s$  是采样频率, $B$  是模拟输

入信号的带宽。上式右边第三项表示增加采样频率(过 采样)可提高信噪比。

### 2.2 有效位数

实际上 ADC 的误差表现为静态及动态非线性误差, 并且动态误差随输入信号压摆率的增加而变大。因此实 际测量的信噪比要比理论上的小一些。计算有效位数 (ENOB)可以从对方程(1)的 N 求解得到。

ENOB(N) =

$$\frac{\text{SNR}(\bar{\mathbf{x}}) - 1.7 \text{dB} - 10 \log(f_s/2B)}{6.02}$$

(2)

采用 DET 技术时,噪声既包括量化噪声,也包括采 样过程中奈奎斯特带宽外的谐波与带宽内信号混迭产生 的噪声。另外,因为正弦信号容易产生和便于数学分析, 所以在评估 ADC 的动态性能时, 它是最常用的信号。

3 用 FFT 法测试 ADC 信噪比及计算有效位数

FFT 是从频域测试 ADC 信噪比的方法,步骤如下:

- (1)用高精度正弦波输入被测 ADC,正弦波频率 f= 1.8625MHz, 采样频率分别为 f<sub>s</sub>=3.725MHz 和 f<sub>s</sub>=7.45 MHz, 正弦波频率小于采样频率的一半、保证不会发生混叠。 用 DSP 顺序记录 ADC 输出数据。

- (2)接着用 DSP 进行 FFT 运算。当数据记录不是包含 整数个信号周期时,要加窗函数来抑制频谱泄漏。可选 择适当的窗函数,使信号能量集中在主瓣内,主瓣外能 量可忽略。

- (3)根据 FFT 运算的结果,首先计算信号的有效值。 然后取基频和其两旁适当数目的采样值,求它们的平方 和的平方根。所需采样的数目由已知的ADC的分辨率 决定。其余的频率采样值的平方和的平方根作为噪声的 有效值,它包括量化噪声、ADC的谐波噪声、超越噪声及 FFT 的舍入误差。有了这两个有效值就能计算 ADC 的 信噪比(SNR):

$$SNR = 20\lg(V_s/V_n) \tag{3}$$

其中,V。表示信号电平的有效值,V。表示噪声电平 的有效值。

(4)计算出信噪比后 (噪声包括高次谐波失真、杂散 波失真和宽带噪声),根据公式(2)即可计算出 ADC 的 有效位数。

## 4 测试结果

利用上述测试系统和测试参数对ADC采样的数据 进行 FFT 运算, 并按上述算法进行计算, 结果表明,在  $f_s = 2f$  时, SNR=67.6dB, 根据公式(2)得出有效位数为:

ENOB(N) =

$$\frac{\text{SNR} ( \mathfrak{F} \overline{k} ) - 1.7 \text{dB} - 10 \text{lg} (f_s / 2B)}{6.02}$$

=  $\frac{67.6 - 1.7}{6.02} = 10.95 \text{ bit}$

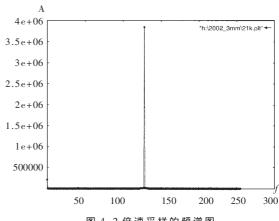

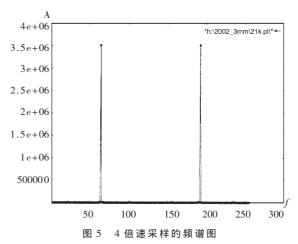

在  $f_s=4f$  时,采样频率提高一倍,SNR=70.3dB,提高了 2.7dB 左右。理论上,采样率提高一倍时,由公式(1)得:  $\Delta$ SNR=10lg( $f_s'/2B$ )-10lg( $f_s/2B$ )=10lg2-10lg1=3dB 即采样率提高一倍、信噪比提高 3dB, 相当于 ADC 有效位数提高半位。可见实际测试数据结果跟理论值基 本吻合。以2倍速采样频率和4倍速采样频率采样后作 FFT 的结果如图 4 和图 5 所示。

图 4 2 倍速采样的频谱图

对于高速 ADC 来说,其动态特性格外重要,因而精 确地测试 ADC 的动态指标成为非常有意义的工作。对 于实时信号处理机而言,ADC模块单元的大动态范围、 高信噪比等显得尤为重要,这些性能将直接影响到后续 的信号处理和检测。因此利用实时信号处理机本身的硬 件平台,通过软件编程来实现对ADC的测试是一种高 效、高精度的方法。

# 参考文献

- 1 Peetz BE.Dynamic Testing of Waveform Records. IEEE Trans Instrum Meas, 1983; 32(1):12

- 2 Clayton C, Mcclean JA, Mccarra GJ. FFT Performance Testing of Data Acquisition Systems. IEEE Trans Instrum Meas, 1986; 35(2): 212

- 3 Jenq YC. Measuring Harmonic Distortion and Noise Floor of an A/ D Converter Using Spectral Avarging. IEEE Trans Instrum Meas, 1988; 37(4):525

- 4 Benetazzo L, Narduzzi C, Offelli Cetal. A/D Converters Performance Analysis by a Frequency-domain Approach. IEEE Trans Instrum Meas, 1990; 39(6):834

(收稿日期:2003-10-10)